许多数据采集、工业控制和仪表应用都需要超高速模数转换器 (ADC),而逐次逼近寄存器 (SAR) 转换器则能完全满足这一要求。然而,我们必须确保 SAR 转换器周围的外部电路也能胜任这一任务,才能确保成功的转换结果。对于 SAR 转换器来说,需要特别注意的关键端子是其模拟信号输入端——如果不加以重视,这些输入引脚会产生稳定性问题和电容电荷"反冲",从而导致转换不准确并延长信号采集时间。

在 SAR 转换器应用中,精确控制输入信号的解决方案在于运算放大器(运放)的驱动。如搭配适当的输出电阻和电容值,这些器件就是高分辨率、16 位和 20 位 SAR 转换器系统的高精度稳健解决方案的基础。

本文将简要讨论实现稳定准确的 SAR ADC 转换的相关问题。然后,介绍一款合适的运放来驱动 SAR ADC,并说明如何实现必要的输入驱动电路。我们将以 Analog Devices 的解决方案为例进行说明。

SAR ADC 输入电路

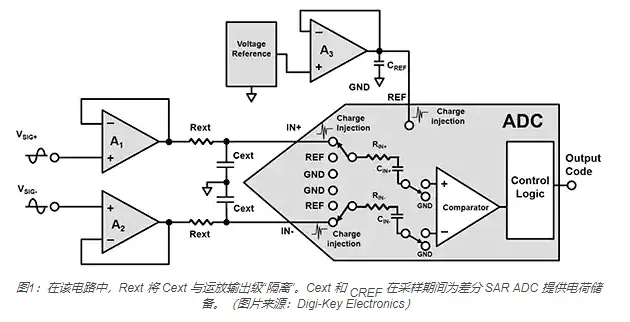

SAR ADC 驱动电路具有将 ADC 与其信号源隔离的运算放大器(A1 和 A2)(图1)。在该电路中,Rext 通过"隔离"放大器的输出级与 ADC 容性负载(CIN+ 和 CIN-)和 Cext 隔离来保持稳定。Cext 和 CREF 为 ADC 提供了一个近乎完美的输入源,可以吸收来自 IN+、IN- 和 REF 输入端子的开关电荷注入。输入端子 (IN+, IN-) 在转换器的采集期间跟踪输入信号 (VSIG+, VSIG-) 的电压,为 ADC 输入采样电容 CIN+ 和 CIN- 充电。

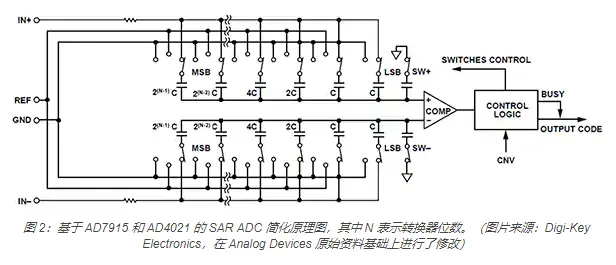

以 Analog Device 的 AD7915 (16 位)和 AD4021(20 位)SAR ADC 为例观察 ADC 内部,可以看到该器件使用了电荷再分配数模转换器 (DAC)。容性 DAC 有两个相同的二元加权电容阵列。这两个电容阵列连接非反相和反相比较器输入端(图 2)。

在采集阶段,输入端(IN+ 和 IN-)切换到电容阵列。此外,SW+ 和 SW- 闭合,将最小有效位 (LSB) 电容与地 (GND) 相连。在这种状态下,电容阵列成为采样电容,采集 IN+ 和 IN- 模拟信号。采集阶段结束后,控制逻辑(右侧)的 CNV 输入变为高电平,启动转换阶段。

转换阶段开始时,先断开 SW+ 和 SW-,将两个电容阵列切换到 GND。在这种配置下,捕获的 IN+ 和 IN- 差分电压会导致比较器变得不平衡。电荷再分配 DAC 在 GND 和 REF 之间有条不紊地将电容器阵列的每个元件从最重要的位 (MSB) 切换到 LSB。比较器输入按二元加权电压步长来变化 (VREF/2N-1, VREF/2N-2...VREF/4, VREF/2)。控制逻辑将开关从 MSB 切换为 LSB,使得比较器回到平衡状态。这个过程结束后,ADC 返回采集阶段,控制逻辑产生 ADC 输出代码。

输入电荷注入、电路稳定性和驱动 AD7915 ADC

转换过程的关键是获取准确的输入信号电压。当驱动放大器准确地向输入电容器 CIN+ 和 CIN- 进行充电时,ADC 数据转换过程就会顺利进行,同时保持稳定,直至 ADC 采集时间结束。对设计者来说,问题在于 ADC 的输入端引入了一个电容 (CIN+, CIN-) 以及需要驱动放大器进行管理的开关噪声或"反冲"电荷注入。

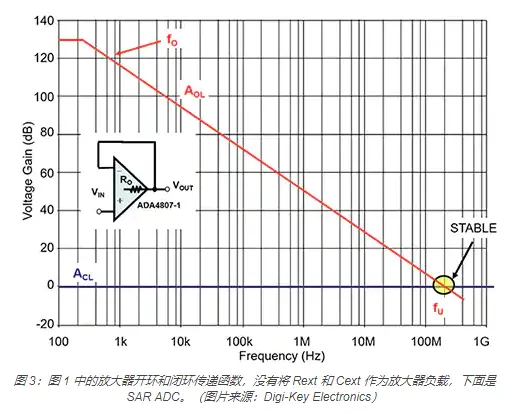

放大电路 Bode plot 可以快速估算电路稳定性。Bode plot 工具可以近似地描述放大器的开环和系统闭环增益传递函数的大小(图 3)。

y 轴量化了放大器电路的开环增益 (AOL) 和闭环增益 (ACL),其中放大器的 AOL 曲线从 130 分贝 (dB) 开始,闭环增益 ACL 等于 0dB。沿 X 轴的单位以对数形式量化了从 100 赫兹 (Hz) 到 1 千兆赫兹 (GHz) 的开环和闭环增益频率。

在图 3 中,放大器在大约 220Hz (fO) 时的直流开环增益以 -20dB/十倍频程的速度从 130dB 下降。随着频率的增加,这种衰减在持续并在大约 180 兆赫兹 (MHz) 时跨过 0dB。由于这条曲线表示单极系统,所以分频器频率 fU 等於单位增益稳定放大器的增益带宽乘积 (GBWP)。该图代表一个稳定的系统,因为 AOL 和 ACL 的截止率是 20dB/十倍频程。

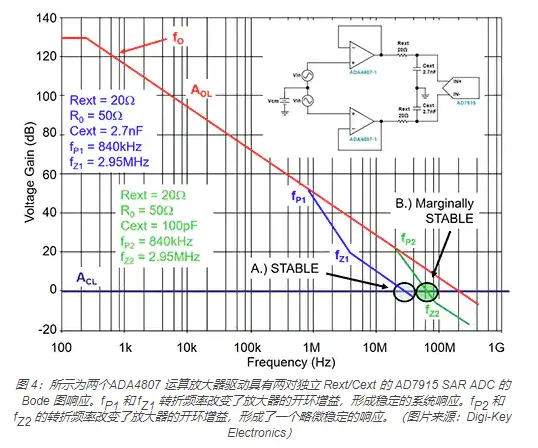

加入 Rext 和 Cext 以及 SAR ADC 后,通过创建系统零点和极点来修改放大器电路(图 4)。该系统包括一个 16 位、每秒 1 兆次 (MSPS) 的 AD7915 差分 PulSAR ADC 和一个 180 MHz、轨至轨输入/输出 ADA4807-1 放大器,该器件由 Analog Devices 提供。由于存在 30 皮法 (pF)(典型值)的 ADC 输入电容负载,放大器和 ADC 的组合需要 Rext。该电路还需要 Cext 作为充电筒,在 ADC 输入端提供足够的电荷,以准确匹配输入电压。

如图 4 所示,由于电路在初始采集时 ADC 的电容负载和 ADC 的开关电荷注入,有可能发生振荡。Rext/Cext 放大器输出元件所产生的额外极点和零点保证了系统稳定,所以开环和闭环增益曲线交点大于 20dB/十倍频程,使相位裕度小于 45°。这种配置与 fP2 和 fZ2 一起构成一个不稳定电路。

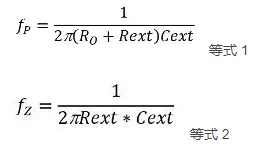

为避免不稳定,在评估电路中带有 Rext 和 Cext 的放大器开环增益曲线时,设计人员需要考虑放大器的开环输出电阻 RO 的影响。阻值为 50 欧姆 (W) 的RO 与 Rext、Cext 的组合通过引入一个极点(fP,公式 1)和一个零点(fZ,公式 2)来修正开环响应曲线。RO、Rext 和 Cext 的值决定了 fP 的转折频率。Rext 和 Cext 的值决定了零转折频率 fZ。

fP 和 fZ 的计算结果是:

fP1 = 842 kHz

fZ1 = 2.95 MHz

其中:RO = 50 W

Rext = 20 W

Cext = 2.7 纳法拉 (nF)

fP2 = 22.7 MHz

fZ2 = 79.5 MHz

其中:RO = 50 W

Rext = 20 W

Cext = 0.1 nF

上述 fP1 和 fZ1 的值使 AD7915 和 ADA4807-1 成为一个稳定的系统。

驱动 Easy Drive AD4021 SAR ADC

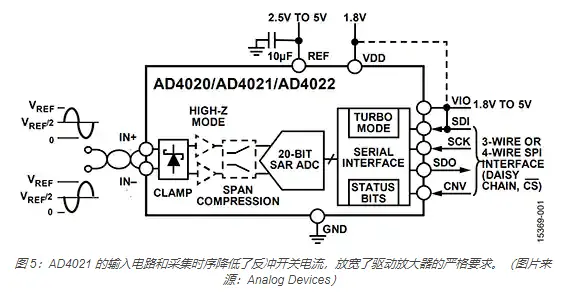

AD7915 的替代产品是 AD4021 20 位 1 MSPS Easy Drive SAR 转换器。AD4021 器件系列将输入反冲和输入电流显著降低至 0.5 微安 (μA)/MSPS。Easy Drive 器件的特点是能降低功耗和信号链复杂性。

AD4021 的模拟输入端采用了能够降低典型开关式电容 SAR 输入非线性电荷反冲的电路。因为减少了反冲并延长了采集阶段,因此可以使用较低带宽、较低功率的驱动放大器(图 5)。

减少反冲并延长采集时间,也使得输入电阻电容 (RC) 滤波器中的 Rext 电阻值增大,Cext 电容相应减小。这种较小的 Cext 放大器负载组合提高了稳定性,降低了功耗。

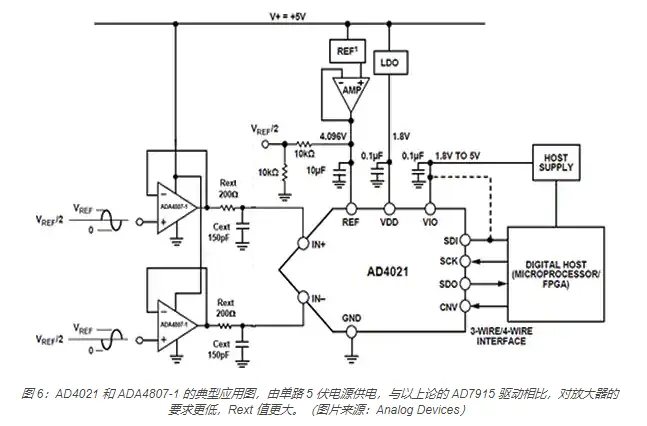

使用单路 5 伏电源的 AD4021 的推荐连接图似乎具有类似电路图。但对放大器的要求降低了,Rext/Cext(R 和 C)的值更小(图 6)。

图 6 中,基于 SAR 的 AD4021 也采用了电荷再分配采样 DAC。ADC 有一个板载转换时钟和串行时钟。因此,转换过程不需要同步时钟 (SCK) 输入。这种时钟配置可以延长采集时间,通过为输入信号提供更长的时间使其建立至最终值,从而提高精度。

AD7915 和 AD4021 的驱动放大器主要考虑的是噪声,因为放大器/Rext/Cext 组合必须从满量程阶跃到 16 位水平 (0.0015%, 15ppm) 的 AD7915,以及 20 位水平 (0.00001%, 1ppm) 的 AD4021。

为了保持 AD7915 和 AD4021 的信噪比( SNR) 性能,驱动放大器的噪声必须小于 ADC 噪声的三分之一。AD4021 的噪声为 60 微伏有效值 (mVrms),这就要求放大器/Rext/Cext 组合的噪声小于 20mVrms。AD4021 的噪声为 31.5 mVrms,这就要求放大器/Rext/Cext 组合的噪声小于10.5 mVrms。

Analog Devices 的精密 ADC 驱动器工具可帮助设计人员快速计算出正确的 Rext 和 Cext 值。通过选定的驱动器和 ADC,该工具可以模拟电路的建立时间、噪声和失真行为。

结语

SAR ADC 将继续在超高速数据采集、工业控制和仪器仪表应用中占据主导地位。然而,我们需要考虑这类器件的外部输入电路——驱动放大器和输入滤波器,以适应潜在的开关电荷注入和放大器稳定性问题。

大多数 SAR 转换器(如 AD7916 和 AD4021)精确控制输入信号的解决方案都依赖运放驱动器,如本示例中的 ADA4807-1。如图所示,这类器件在适当的输出电阻和电容值的支持下形成一个坚实的基础,然后在此基础上建立一个高精度、稳健、高分辨率、16 位或 20 位 SAR 转换器系统。

来源:Digi-Key

声明:本文由作者原创,文章内容系作者个人观点,电子发烧友网转载仅作为传达一种不同的观点,不代表电子发烧友网对该观点的赞同或支持,如有异议,欢迎联系电子发烧友网。

更多热点文章阅读

转载请超链接注明:头条资讯 » 模拟基础知识:处理 SAR ADC 输入驱动难题

免责声明

:非本网注明原创的信息,皆为程序自动获取互联网,目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责;如此页面有侵犯到您的权益,请给站长发送邮件,并提供相关证明(版权证明、身份证正反面、侵权链接),站长将在收到邮件24小时内删除。