來源:內容由半導體行業觀察(ID:icbank)編譯自「erik-engheim」,謝謝。

到目前為止,很明顯,蘋果的M1芯片是一件大事。而且,對其他行業的影響也越來越清晰。在這個故事中,我想談談這件事對RISC-V微處理器的影響,而這對於大多數讀者而言可能並不明顯。

首先讓我為您提供一些背景知識:《蘋果M1為什麼那麼快》,在那個故事中,我談到了驅動M1性能的兩個因素。一種是使用大量的解碼器和亂序執行(OoOE)。

接下來的故事將與另一部分有關,那就是異構計算。Apple積極追求添加專用硬件單元的策略,在本文中,我將其稱為協處理器:

GPU(圖形處理單元),用於圖形和許多其他具有大量數據並行性的任務(同時對多個元素執行相同的操作)。

神經引擎。用於機器學習的專用硬件。

用於圖像處理的數字信號處理硬件(DSP)。

硬件中的視頻編碼。

在蘋果的解決方案中,他們並沒有添加更多的通用處理器,而是開始在解決方案中添加更多的協處理器。在這裡,您也可以使用專用的術語——加速器。

這不是一個全新的趨勢,我從1985年開始使用的老式Amiga 1000具有協處理器來加速音頻和圖形。現代GPU本質上是協處理器。Google的Tensor處理單元是一種用於機器學習的協處理器。

Google TPU是專用集成電路(ASIC)。我將它們稱為協處理器

什麼是協處理器?

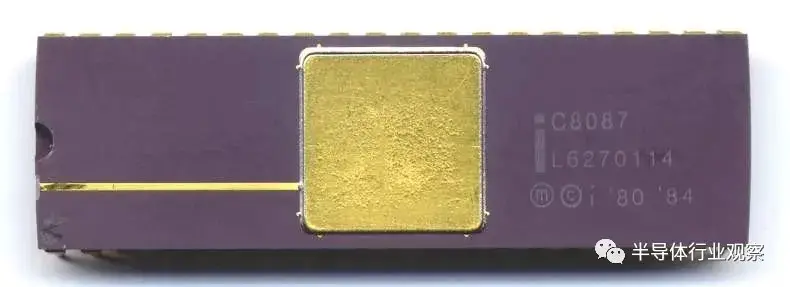

與CPU不同,協處理器不能單獨存在。您不能僅通過將協處理器插入其中來製造計算機。協處理器作為專用處理器,可以很好地完成特定任務。協處理器的最早示例之一是Intel 8087浮點單元(FPU)。不起眼的Intel 8086微處理器可以執行整數運算,但不能執行浮點運算。有什麼不同?

英特爾8087。一種用於執行浮點計算的早期協處理器

整數是這樣的整數:43, -5, 92, 4。

這些對於計算機來說相當容易使用。您可能會自己組合一個解決方案,以使用一些簡單的籌碼相加整數。但當您需要小數時,問題就開始了。

假設您要對類似4.25, 84.7 or 3.1415這樣的數字進行加法或乘法運算。因為這些是浮點數的示例。如果該點之後的位數是固定的,我們將其稱為固定點號。金錢常常被這樣對待。您通常在該點後有兩位小數。

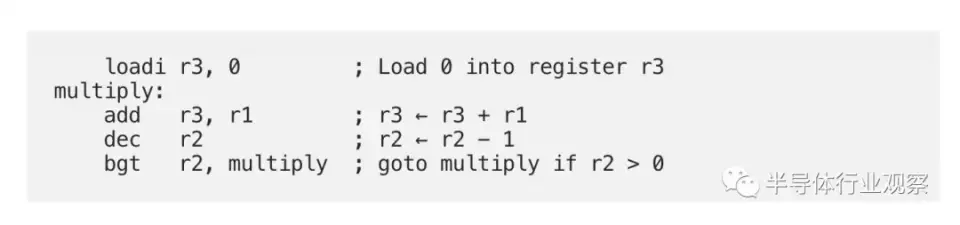

當然,您可以使用整數來模擬浮點運算,但是速度較慢。這類似於早期的微處理器也不能夠將整數相乘。他們只能加減。但是,仍然可以執行乘法。您只需要模擬它將添加多個內容。例如3 × 4簡單4 + 4 + 4。

理解下面的代碼示例並不重要,但是它可以幫助您瞭解CPU如何僅通過使用加,減和分支(代碼跳轉)來執行乘法。

簡而言之,您總是可以通過重複簡單的運算來實現更復雜的數學運算。

所有協處理器的工作與此相似。CPU總是有一種方法可以完成與協處理器相同的任務。但是,這通常需要重複多個更簡單的操作。我們之所以提早使用GPU是因為,對數百萬個多邊形或像素重複相同的計算對於CPU來說確實很耗時。

如何與協處理器傳輸數據

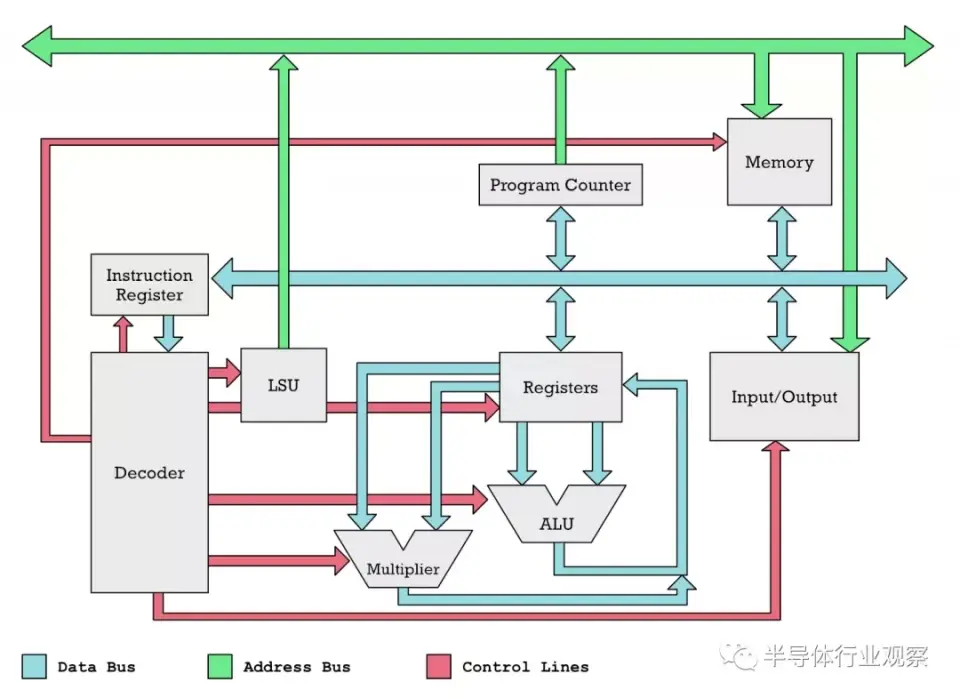

讓我們看一下下面的圖,以更好地瞭解協處理器是如何與微處理器(CPU)或通用處理器一起工作。

微處理器工作原理概述。數字沿彩色線移動。輸入/輸出可以是協處理器,鼠標,鍵盤和其他設備。

我們可以將綠色和淺藍色的總線視為管道。通過這些管道,我們可以將數字推送到CPU的不同功能單元(繪製為灰色框)。這些盒子的輸入和輸出連接到這些管道。您可以認為每個盒子的輸入和輸出都有閥門(( valves))。紅色控制線用於打開和關閉這些閥(( valves))。因此,負責紅線的解碼器可以打開兩個灰色框上的閥(valves),使數字在它們之間流動。

您可以將數據總線視為帶有由紅色控制線打開和關閉的閥門( valves)的管道。但是,在電子設備中,這是通過我們所謂的多路複用器完成的,而不是實際的閥門。

這讓我們解釋瞭如何從內存中獲取數據。要對數字執行運算,我們需要在寄存器中進行操作。

該解碼器使用控制線,以打開灰色存儲器框和寄存器框的閥門( valves)。具體是這樣的:

1、解碼器打開負載存儲單元(Load Store Unit :LSU)上的閥,該閥使內存地址從綠色地址總線上流出。

2、內存盒上的另一個閥門被打開,因此它可以接收地址。它由綠色管道(地址總線)傳送。所有其他閥都關閉,因此例如輸入/輸出無法接收地址。

3、選擇具有給定地址的存儲單元。它的內容流出到藍色數據總線上,因為解碼器已經打開了通往數據總線的閥門。

4、存儲單元中的數據可以流到任何地方,但是解碼器僅打開了寄存器的輸入閥。

諸如鼠標,鍵盤,屏幕,GPU,FPU,神經引擎和其他協處理器之類的東西都等於“輸入/輸出”框。我們像訪問存儲位置一樣訪問它們。硬盤驅動器,鼠標,鍵盤,網卡,GPU,DMA(直接內存訪問)和協處理器都具有映射到它們的內存地址。

通過指定地址,我們可以像訪問存儲位置一樣訪問硬件。

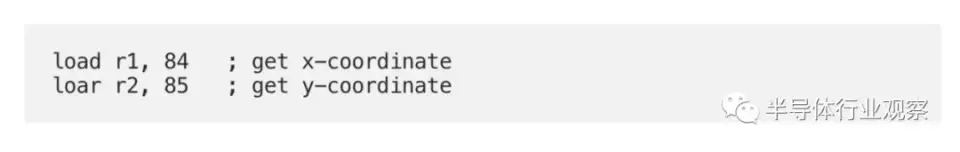

通過這些舉例,你能看懂我到底想說明什麼?如果沒有,讓我補充一些地址。如果處理器嘗試從內存地址84讀取,則可能意味著計算機鼠標的x座標。雖然說85表示y座標。因此,要獲取鼠標座標,您可以在彙編代碼中執行以下操作:

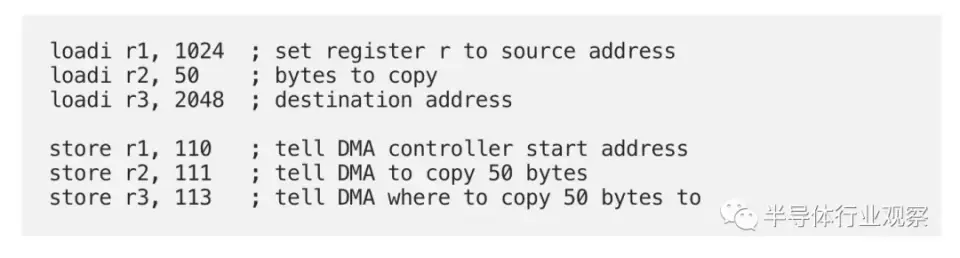

對於DMA控制器,可能會有地址110、111和113,這是特殊含義。這是一個不切實際的彙編代碼程序,使用該程序與DMA控制器進行交互:

一切都以這種方式工作。您讀寫特殊的內存地址。當然,常規的軟件開發人員從來沒有看到過這種情況。這些工作由設備驅動程序完成。您使用的程序只能看到不可見的虛擬內存地址。但是驅動程序會將這些地址映射到其虛擬內存地址。

我不會過多地談論虛擬內存。本質上,我們得到了真實的地址。綠色總線上的地址將從虛擬地址轉換為實際物理地址。當我開始在DOS中使用C / C ++進行編程時,沒有這種東西。我可以將C指針設置為直接指向視頻內存的內存地址,然後開始直接向其寫入以更改圖片。

協處理器的工作方式與此相同。

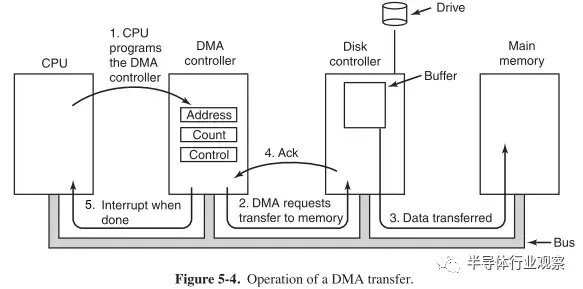

神經引擎,GPU,安全區域等將具有您與之通信的地址。瞭解這些以及諸如DMA控制器之類的重要信息是讓它們可以異步工作。

這意味著CPU可以為神經引擎或GPU安排一堆完整的指令,並將其寫入內存中的緩衝區。然後,通過與它們的IO地址進行對話,將這些指令的位置通知神經引擎或GPU協處理器。

您不希望CPU坐在那裡閒置等待協處理器檢查所有指令和數據。您也不想使用DMA進行操作。這就是為什麼通常您可以提供某種中斷的原因。

中斷如何工作?

在實際操作中,當您在PC中插入各種卡(無論是圖形卡還是網卡)後,它們都將獲得分配一些中斷線。就像一條直線直接進入您的CPU。激活此行後,CPU會將其持有的所有內容都丟棄以處理中斷。

或更具體地說。它在內存中存儲其當前位置及其寄存器的值,因此可以返回到以後執行的操作。

接下來,它在所謂的中斷表中查找要做什麼。該表具有觸發該中斷時要運行的程序的地址。

作為程序員,您不會看到這些東西。對您來說,它看起來更像是為某些事件註冊的回調函數。驅動程序通常在較低級別上進行處理。

我為什麼要告訴你所有這些書呆子的細節?因為它有助於您瞭解使用協處理器時發生的情況。否則,不清楚與協處理器進行通信實際上需要做什麼。

使用中斷可以使許多事情並行發生。當CPU被計算機鼠標中斷時,應用程序可能會從網卡獲取圖像。鼠標已移動,我們需要新的座標。CPU可以讀取這些並將它們發送到GPU,因此可以在新位置重新繪製鼠標光標。當GPU繪製鼠標光標時,CPU可以開始處理從網絡檢索到的圖像。

同樣,通過這些中斷,我們可以將複雜的機器學習任務發送給M1神經引擎,以識別網絡攝像頭上的人臉。同時,計算機的其餘部分都響應,因為神經引擎正在與CPU所做的其他所有事情並行地瀏覽圖像數據。

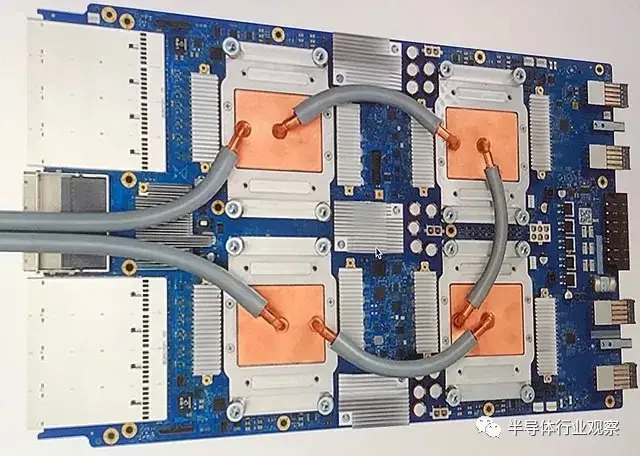

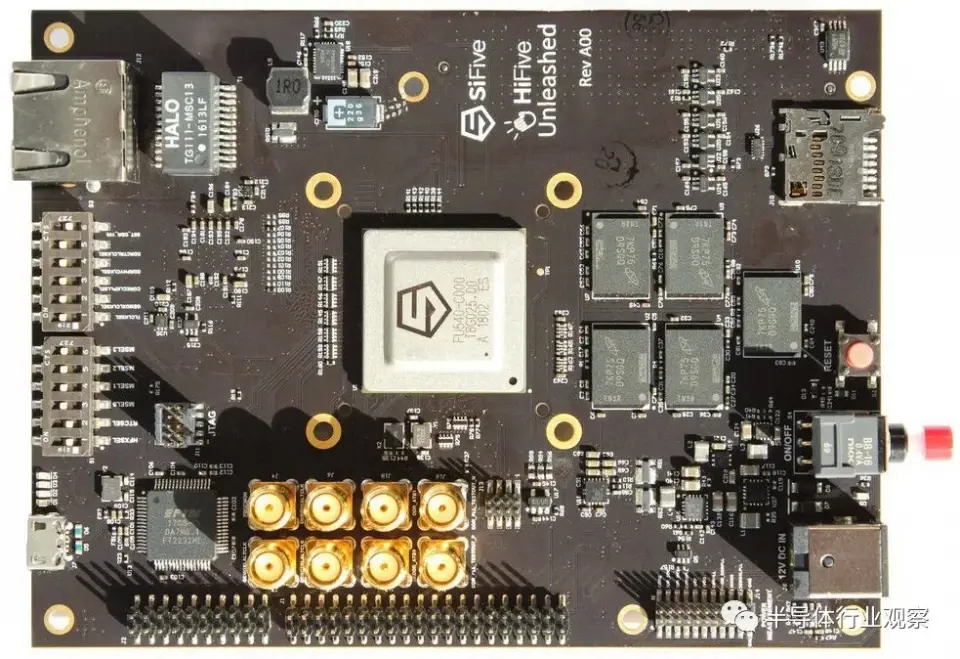

SiFive的基於RISC-V的板能夠運行Linux

RISC-V的興起

早在2010年,在加州大學伯克利分校的並行計算實驗室( Parallel Computing Laboratory),我們看到了向大量使用協處理器發展的趨勢。因為他們看到,當摩爾定律走向終結時,意味著您不再能夠輕易地從通用CPU內核中擠出更多性能。因此您需要專用的硬件:協處理器。

讓我們暫時反思一下為什麼。我們知道,時鐘頻率不能輕易增加,我們被困在3–5 GHz這個頻率範圍很久了。任何頻率的升高都會帶來能量消耗和熱量小號。

但是,我們可以添加更多的晶體管,不過我們根本無法使晶體管工作得更快。因此,我們需要並行進行更多工作。一種方法是添加大量通用內核。正如我之前討論的那樣,我們可以添加很多解碼器並執行亂序執行(OoOE)。

晶體管預算:CPU內核還是協處理器?

您可以繼續傳統玩法,讓你的CPU最終擁有128個通用內核,例如Ampere Altra Max ARM處理器。但這真的是我們硅的最佳用途嗎?毫無疑問,對於雲中的服務器而言,這很棒。因為我們可以使所有這128個內核忙於處理各種客戶端請求。但是,臺式機系統可能無法有效地在普通臺式機工作負載上使用8個以上的內核。因此,如果您說32核,則是浪費了很多時間會閒置的許多核上的硅。

與其將所有的芯片都花在更多的CPU核上,不如我們可以添加更多的協處理器?

這樣考慮:您有一個晶體管預算。在早期,也許您的預算為2萬個晶體管,並且您認為可以使CPU具有15000個晶體管。這在80年代初已經接近現實。現在,該CPU可以執行100個不同的任務。假設為其中一項任務製作專用的協處理器,將花費1000個晶體管。如果您為每個任務創建一個協處理器,那麼您將獲得10萬個晶體管。那會浪費你的預算。

晶體管豐度變化策略

因此,在早期設計中,需要專注於通用計算。但是今天,我們可以用許多晶體管填充芯片,我們幾乎不知道該怎麼辦。

因此,設計協處理器已成為一件大事。進行各種新型協處理器的研究很多。但是,這些往往包含漂亮卻笨拙的加速器,這需要改進。與CPU不同,它們無法讀取告訴他們所有步驟的指令。他們通常不知道如何訪問內存和組織任何事情。

因此,對此的常見解決方案是使用簡單的CPU作為一種控制器。因此,整個協處理器是由一個簡單的CPU控制的專用加速器電路,該電路配置加速器以完成其工作。通常這是高度專業化的。例如,諸如神經引擎或張量處理單元之類的東西處理的是非常大的寄存器,可以容納矩陣(行和數字列)。

量身定製的RISC-V以控制加速器

這正是RISC-V設計的目的。它僅有約40至50條指令的最小指令集,這使其可以執行所有典型的CPU工作。聽起來可能很多,但是請記住,x86 CPU具有超過1500條指令。

與大量的固定指令集不一樣,RISC-V是圍繞擴展的概念設計的。每個協處理器都是不同的。因此,它將包含一個RISC-V處理器來管理實現核心指令集的事物以及針對該協處理器需要做什麼而定製的擴展指令集。

好吧,現在也許您開始看到我正在瞭解的輪廓。蘋果的M1確實將推動整個行業朝著這個協處理器主導的未來發展。為了製造這些協處理器,RISC-V將成為解決難題的重要組成部分。

但為什麼?製作協處理器的每個人都不能只是發明自己的指令集嗎?畢竟,我認為蘋果已經做到了。或者可能他們使用ARM。我不知道。如果有人知道,請給我打個電話。

堅持使用RISC-V進行協處理器設計有什麼好處?

製造芯片已成為一件複雜而昂貴的事情。建立工具以驗證您的芯片。運行測試程序,診斷和許多其他事情需要很多努力。這是當今使用ARM的價值的一部分。他們擁有龐大的工具生態系統,可幫助您驗證設計並對其進行測試。

因此,尋求定製的專有指令集不是一個好主意。但是,使用RISC-V可以為多家公司提供標準工具。突然有一個生態系統,多家公司可以分擔負擔。

但是,為什麼不使用現有的ARM呢?您會看到ARM被製成通用CPU。它具有較大的固定指令集。在客戶和RISC-V競爭的壓力下,ARM放鬆了態度,並於2019年開放了擴展指令集。但這仍然存在的問題是,因為它不是一開始就為此目的而設計的。整個ARM工具鏈將假定您已實現了整個大型ARM指令集。這對於Mac或iPhone的主CPU來說很好。

但是對於協處理器,您不需要或不需要這麼大的指令集。您需要一個圍繞最小擴展基礎固定擴展指令集這一思想構建的工具生態系統。

為什麼會有這樣的好處?英偉達對RISC-V的使用提供了一些見識。在大型GPU上,他們需要某種通用CPU用作控制器。但是,他們可以為此預留一定數量的硅,並且允許產生的熱量極小。請記住,許多事物正在爭奪空間。

RISC-V的小而簡單的指令集使其可以以以比ARM少得多的硅實現RISC-V內核。

由於RISC-V的指令集如此小而簡單,因此它擊敗了包括ARM在內的所有競爭對手。Nvidia發現,選擇RISC-V可以製造出比其他任何產品都小的芯片。他們還將功耗降至最低。

因此,通過擴展機制,您可以將自己限制為僅添加對您需要完成的工作至關重要的指令。用於GPU的控制器可能需要除加密協處理器上的控制器以外的其他擴展。

ARM將成為新的x86

因此,具有諷刺意味的是,我們可能會看到Mac和PC由ARM處理器驅動的未來。但是在所有定製硬件周圍,所有協處理器將由RISC-V主導。隨著協處理器越來越流行,片上系統(SoC)中的硅芯片可能是運行RISC-V,而不是Arm。

當我寫上面的故事時,我實際上並沒有完全理解RISC-V的全部含義。儘管未來將與ARM或RISC-V有關。相反,它可能是ARM和RISC-V。

ARM指揮RISC-V協處理器大軍

通用ARM處理器將會是RISC-V驅動的協處理器的中心,以加速從圖形,加密,視頻編碼,機器學習,信號處理到處理網絡程序包的所有可能任務。

David Patterson教授和他在加州大學伯克利分校的團隊看到了這一未來的來臨,這就是RISC-V如此精心定製以迎接這個新世界的原因。我們看到RISC-V在各種專用硬件和微控制器中得到了如此廣泛的應用和關注,我認為當今ARM主導的許多領域都將成為RISC-V的天下。

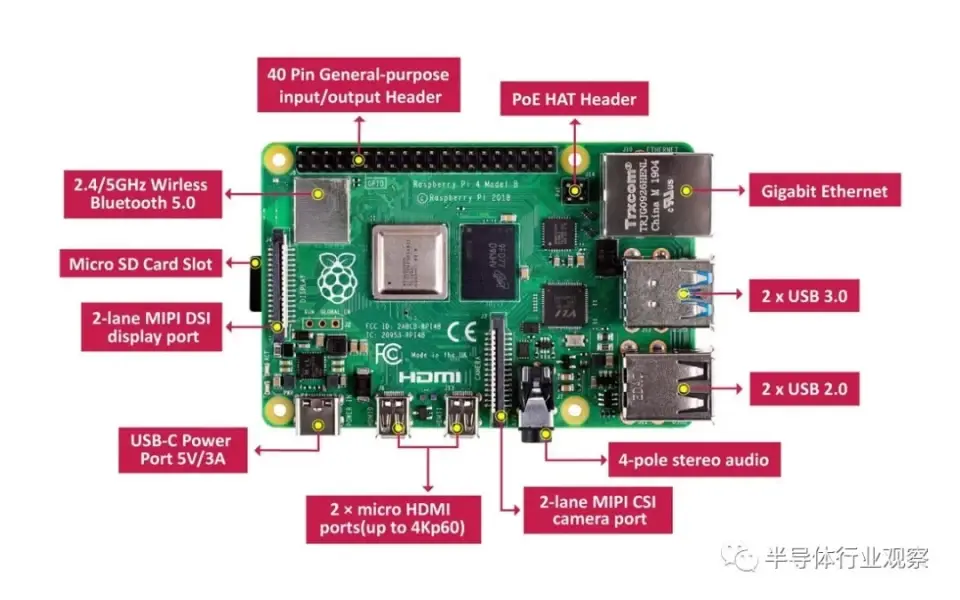

Raspberry Pi 4微控制器,當前使用ARM處理器

想象一下類似Raspberry Pi的東西。現在它運行在ARM芯片上。但是未來的RISC-V變體可能會提供滿足不同需求的大量變體。可能有機器學習微控制器。另一個可以是面向圖像處理的。三分之一可能用於加密。基本上,您可以選擇帶有自己風格的微控制器。您可能可以在其上運行Linux並執行所有相同的任務,只是性能配置文件會有所不同。

具有特殊機器學習指令的RISC-V微控制器將比具有視頻編碼指令的RISC-V微控制器更快地訓練神經網絡。

英偉達已經通過他們的Jetson Nano冒險走這條路,如下所示。它是Raspberry Pi大小的微控制器,具有用於機器學習的專用硬件,因此您可以執行對象檢測,語音識別和其他機器學習任務。

NVIDIA Jetson Nano開發者套件

RISC-V作為主CPU?

許多人問:為什麼不用RISC-V完全替代ARM?儘管其他人則認為這將永遠無法實現,因為RISC-V具有“微妙且簡單”的指令集,無法提供ARM和x86提供的那種高性能。

是的,您可以使用RISC-V作為主處理器。性能也不能阻止我們這樣做。就像使用ARM一樣,我們只需要有人來製造高性能RISC-V芯片。實際上,它可能已經完成了。之前又一家公司已經生成,他們新的RISC-V CPU獲得了創紀錄的每瓦性能。

常見的誤解是複雜的指令可以提供更高的性能。RISC工作站在90年代就證明瞭這一點,因為它們破壞了性能基準測試中的x86計算機。英特爾在90年代也戰勝了很多RISC工作站。實際上,RISC-V有很多巧妙的竅門來獲得高性能。

簡而言之,沒有理由不能使您的主CPU成為RISC-V處理器,但這也是一個動力問題。MacOS和Windows已在ARM上運行。至少在短期內,微軟或蘋果公司是否會花費精力進行另一次硬件過渡似乎值得懷疑。

分享你的意見

讓我知道你的想法。這裡有很多事情很難猜測。我們看到,例如,現在有人聲稱RISC-V CPU在功耗和性能方面確實勝過ARM。這也使您想知道RISC-V是否確實有可能成為計算機的中央CPU。

我必須承認,為什麼RISC-V會勝過ARM尚不為人所知。經他們自己承認,RISC-V是一個相當保守的設計。他們使用的指令不多,而其他一些較舊的設計尚未使用過。

但是,將所有內容配對到最小似乎是一個很大的收穫。這使得可以實現非常小的和簡單的實現或RISC-V CPU。這再次使得可以減少瓦特使用並增加時鐘頻率。

因此,關於RISC-V和ARM的未來,尚未定局。

轉載請超鏈接註明:頭條資訊 » 蘋果M1預示著RISC-V的崛起?

免責聲明

:非本網註明原創的信息,皆為程序自動獲取互聯網,目的在於傳遞更多信息,並不代表本網贊同其觀點和對其真實性負責;如此頁面有侵犯到您的權益,請給站長發送郵件,並提供相關證明(版權證明、身份證正反面、侵權鏈接),站長將在收到郵件24小時內刪除。